# Performance Analysis of Packed U-cell Multilevel Topology with Various Multicarrier Sine PWM Schemes

Niraj Kumar Dewangan, Student Member, IEEE, Pallavee Bhatnagar, Member, IEEE, Gurpreet Singh

Abstract—Multilevel DC to AC conversion is an attractive solution for high/medium power applications with improved power quality as compared to the classic two-level solution. Avenues are being also sought for implementing multilevel inverters for low power applications. Overall component count in conventional topologies is very high especially for a large number of output levels for enhanced power quality. Thus, modifications are being carried out in conventional topologies so as to reduce overall component count. In this paper, three such modified topologies are analysed in order to understand the possible pros and cons. Comments are made based on important qualitative and quantitative features. Simulation results are presented wherever necessary.

Index Terms—Classical topologies, multilevel inverter, pulse width modulation (PWM), reduced component count, total harmonic distortion (THD).

### I. INTRODUCTION

Multilevel voltage source inverters have emerged as an effective solution for high power DC to AC conversion applications [1]. A multilevel inverter (MLI) comprises of multiple input DC levels (obtained from DC sources and/or capacitors) and power semiconductor devices to synthesize a stepped waveform. Blocking voltage requirements for the power switches are lower as compared to the overall operating voltage level [2]. In addition, the multilevel waveform exhibits better harmonic profile as compared to the conventional two-level waveform. Some other important advantages of MLIs are: reduced dv/dt stress on the load and possibility of fault tolerant operation [3]. Recent trends indicate that MLIs can also be employed for low power applications [4].

Quality of the multilevel waveform is further enriched by

Dr. K.K. Gupta and Dr. P. Bhatnagar are with Jai Narain College of Technology (J.N.C.T.), Bhopal (M.P.)  $462\ 036$  India (e-mail: kk\_mact@rediffmail.com, pallaveebhatnagar9@gmail.com) (contact no.: +91-9009231797).

increasing the number of levels. This, however, inadvertently leads to the requirement of a large number of power semiconductor devices (accompanied with respective gate driver circuits). Thus system complexity and cost increase and overall system reliability and efficiency worsen. For high resolution waveform (implying a much better power quality), practical considerations necessitate reduction in overall component count [5].

The so-called 'conventional (or classic)' multilevel topologies which have been extensively studied and are commercially available are: neutral point clamped (NPC), cascaded H-bridge (CHB) and flying capacitors (FC) converters [1, 3, 5-7]. These topologies exhibit a significant increase in the number of power switches, number of switches conducting simultaneously and overall cost of the system with the increase in the number of output levels. Researchers, therefore, continue to focus on reducing the component count in multilevel topologies through modifications in the conventional topologies. These modifications can be primarily characterized as: use of asymmetric sources [13-15] topological changes [8-12]; and combination of topological changes and asymmetric source configurations [16-18].

In this paper, one example each from the aforesaid modification strategies are studied and important observations are derived regarding reduction in component count, possibility of power balancing and optimal switching of power devices. Accordingly, the modified topologies may or may be employed depending on the application requirements.

The paper is organized as follows. Section II of the paper presents a general introduction on improvement of power quality through multilevel waveforms. Example of employing asymmetric source configuration in the classic cascaded H-bridge topology is presented in Section III. In Section IV, a modified H-bridge topology with an auxiliary bidirectional switch is discussed. A modified topology based on the flying capacitor structure which also employs asymmetric source configuration is analysed in Section V. Concluding remarks and inferences are summarized in Section VI.

waveforms.

### II. POWER QUALITY IMPROVEMENT

Power quality is quantitatively judged through a factor called 'total harmonic distortion (THD)' and through the presence of lower order harmonics which directly affect the filter size. Based on the type of output waveform, inverters can be classified as: square wave, quasi square wave, PWM and multilevel inverters. Because of their poor quality, square wave and quasi square wave inverters are not used for medium/high power applications. These inverters require bulky filters since the lower order harmonics are prominently present. A PWM inverter is controlled so as to imitate a pure

Mag (% of Fundamental)

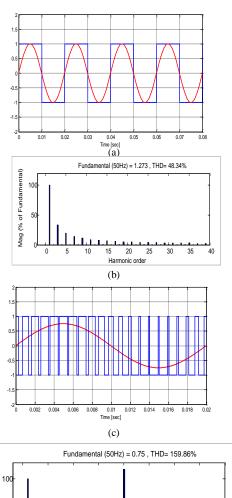

Fig.1. Waveforms and harmonic profiles for: square waveform; two-level PWM waveform: and nine-level waveform.

sine wave, thereby reducing the lower order harmonics, though the higher order harmonics become more prominent. A multilevel waveform further reduces the presence of both lower order and higher order harmonics (thereby reducing the overall THD). Waveforms shown in Fig.1 corroborate these observations.

5 20 25 Harmonic order (d)

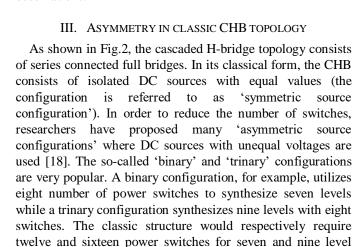

Fig.2. Cascaded H-Bridge topology

This reduction in number of switches has some important fallout. The asymmetric CHB structure becomes non-modular since differently rated switches are used. Modularity has been an important feature of the CHB topology. In addition, equal load sharing amongst the input DC sources cannot be programmed since the sources have different voltages and equal average currents cannot be derived without negatively affecting the output waveform.

## IV. H-BRIDGE STRUCTURE WITH AUXILIARY BIDIRECTIONAL SWITCH

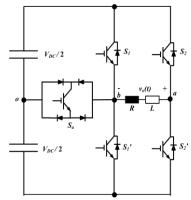

An interesting modification in the standard H-bridge structure is presented in [8] wherein an auxiliary bidirectional-conducting-bidirectional-blocking switch is added to increase the number of levels. The structure is shown in Fig.3.

Fig.3. Modified H-bridge structure for a five-level output

While the standard H-bridge can synthesize two- or three-level waveform, the modified topology can synthesize five levels with the addition of just one switches. The classic CHB structure require eight switches for synthesizing five levels while the modified structure needs only five switches.

An important limitation of the modified topology is that it inadvertently requires a mix of unidirectional and bidirectional power switches, thereby posing design issues. In addition, the input DC sources mandatorily need to be symmetric. Also, no power balancing scheme can be implemented as the topology does not permit so.

### VI. THE PACKED U-CELL TOPOLOGY

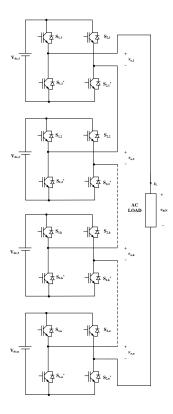

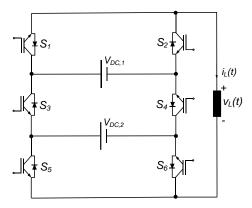

In [16], Youssef Ounejjar et al. have proposed a new power multilevel converter topology that is very competitive compared to the classical topologies. It consists of the so-called 'packed U cells'. Each U cell consists of an arrangement of two power switches and one DC input level (obtained with a voltage source or a floating capacitor). Authors claim that the topology offers high energy conversion quality using a small number of active and passive devices and consequently, has very low production cost. A single-phase structure of the packed U-cell topology with two input DC levels viz.  $V_{DC,1}$  and  $V_{DC,2}$ , and six switches  $S_j$  {j = 1 to 6}, is shown in Fig.4.

The topology is very simple in terms of interconnection of components. The minimal voltage blocking capability required for switches  $(S_1, S_2)$  is  $V_{DC,I}$ , while that for  $(S_5, S_6)$  is  $V_{DC,2}$ . Voltage blocking capability for switches  $(S_3, S_4)$  is  $(V_{DC,I} - V_{DC,2})$ . All the switches, when conducting, should be able to carry the load current. Various states for the structure are shown in Table I. Thus, to obtain a desired voltage level, only three switches conduct simultaneously. It is important to observe from Table I that to derive desired benefit from the topology, symmetric source configuration cannot be used as the output will be a three-level with many redundant states.

Fig. 4. Packed U-cell multilevel inverter topology as proposed in [16]

TABLE I Switching states for topology shown in Fig.4

| State | Output Voltage v <sub>L</sub> (t) | Switches in ON state<br>(other switches remain OFF) |

|-------|-----------------------------------|-----------------------------------------------------|

| 1     | 0                                 | $S_1$ , $S_3$ , $S_5$                               |

| 2     | 0                                 | $S_2, S_4, S_6$                                     |

| 3     | $V_{DC,1}$                        | $S_1$ , $S_4$ , $S_6$                               |

| 4     | $V_{DC,2}$                        | $S_1$ , $S_3$ , $S_6$                               |

| 5     | $V_{DC,1}-V_{DC,2}$               | $S_1$ , $S_4$ , $S_5$                               |

| 6     | $-V_{DC,I}$                       | $S_2$ , $S_3$ , $S_5$                               |

| 7     | $-V_{DC,2}$                       | $S_2$ , $S_4$ , $S_5$                               |

| 8     | $-V_{DC,1} + V_{DC,2}$            | $S_2, S_3, S_6$                                     |

In fact, in [16], authors have proposed an elaborate methodology to calculate the asymmetric voltage levels. For two input levels, the number of output levels can be maximized with  $V_{DC,I} = 3V_{DC}$  and  $V_{DC,2} = V_{DC}$ , however this trinary configuration synthesizes seven levels and not nine, because of the absence of additive combination. Thus for more number of input sources, trinary source configuration is not applicable. Hence, to derive optimal benefit from this topology, employing asymmetric source configuration is binding. For a structure with two input sources, switching of middle two switches viz.  $(S_3, S_4)$  can be performed at fundamental frequency as demonstrated in [16]. This feature, however, is not feasible for packed U cell based structures with more than two number of input DC levels. In [16], the authors implement source  $V_{DC,2}$  with a floating capacitor in which the voltage is maintained at one-third of the voltage level  $V_{DC,1}$ . The control scheme, though, is fairly complex in nature.

### VI. CONCLUSION

As multilevel inverters are gaining interest, efforts are being directed to reduce the device count for increased number of output levels. The merit of a multilevel inverter is enhanced by increasing the number of output levels but it inadvertently leads to increased number of components. Various approaches

to reduce component count, taken by the researchers can be grouped as:

- a. Topological modifications;

- Employing asymmetric source configurations or asymmetric ratios of capacitor voltages; and

- c. Combination of (a) and (b).

The attempt to reduce number of semiconductor switches in multilevel inverters involves one or more of the following compromises/challenges:

- i. Increased power rating of semiconductor switches.

- ii. Increased number of sources.

- iii. Loss of modularity (as happens in asymmetric CHB topology).

- Reduced number of redundant states (as happens in asymmetric configurations).

- v. Complex modulation / control schemes.

- vi. Difficulty in possibility of charge balance control (especially in open loop mode).

Thus, implementing a modified topology would inculcate its own pros and cons and the application requirements would primarily govern the topology which has to be used.

#### REFERENCES

- [1] K.K.Gupta, A. Ranjan, P. Bhatnagar, L.K.Sahu and S.Jain, "Multilevel Inverter Topologies with Reduced Device Count: A Review," *IEEE Transactions on Power Electronics*, vol. 31, no. 1, pp. 135-151, Jan. 2016.

- [2] Buticchi, G.; Lorenzani, E.; Franceschini, G.;, "A Five-Level Single-Phase Grid-Connected Converter for Renewable Distributed Systems," IEEE Transactions on Industrial Electronics, vol.60, no.3, pp.906-918, March 2013.

- [3] K. K. Gupta and S. Jain, "A Novel Multilevel Inverter Based on Switched DC Sources," in *IEEE Transactions on Industrial Electronics*, vol. 61, no. 7, pp. 3269-3278, July 2014.

- [4] De, S.; Banerjee, D.; Siva Kumar, K.; Gopakumar, K.; Ramchand, R.; Patel, C.; , "Multilevel inverters for low-power application," *IET Power Electronics*, vol.4, no.4, pp.384-392, April 2011.

- [5] Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Pérez, M.A.; , "A Survey on Cascaded Multilevel Inverters," *IEEE Transactions* on *Industrial Electronics*, vol.57, no.7, pp.2197-2206, July 2010.

- [6] K. K. Gupta and S. Jain, "Multilevel inverter topology based on series connected switched sources," in *IET Power Electronics*, vol. 6, no. 1, pp. 164-174, Jan. 2013.

- [7] Tolbert, L.M.; Peng, F.Z.; , "Multilevel converters as a utility interface for renewable energy systems," *IEEE Power Engineering Society Summer Meeting*, 2000, vol.2, no., pp.1271-1274 vol. 2, 2000.

- [8] Ceglia, G.; Guzman, V.; Sanchez, C.; Ibanez, F.; Walter, J.; Gimenez, M.I.; , "A New Simplified Multilevel Inverter Topology for DC -AC Conversion," Power Electronics, IEEE Transactions on , vol.21, no.5, pp.1311-1319, Sept. 2006.

- [9] Hinago, Y.; Koizumi, H.; , "A Switched-Capacitor Inverter Using Series/Parallel Conversion With Inductive Load," *IEEE Transactions on Industrial Electronics*, vol.59, no.2, pp.878-887, Feb. 2012.

- [10] Sung-Jun Park; Feel-Soon Kang; Man Hyung Lee; Cheul-U Kim; , "A new single-phase five-level PWM inverter employing a deadbeat control scheme," *IEEE Transactions on Power Electronics*, vol.18, no.3, pp. 831-843, May 2003.

- [11] Gui-Jia Su; , "Multilevel DC-link inverter," IEEE Transactions on Industry Applications, vol.41, no.3, pp. 848-854, May-June 2005.

- [12] Najafi, E.; Yatim, A. H. M.;, "Design and Implementation of a New Multilevel Inverter Topology," *IEEE Transactions on Industrial Electronics*, vol.59, no.11, pp.4148-4154, Nov. 2012.

- [13] Pereda, J.; Dixon, J.; "High-Frequency Link: A Solution for Using Only One DC Source in Asymmetric Cascaded Multilevel Inverters," *IEEE Transactions on Industrial Electronics*, vol.58, no.9, pp.3884-3892, Sept. 2011.

- [14] T. A. Lipo and M. D. Manjrekar, "Hybrid topology for multilevel power conversion," U.S. Patent 6 005 788, Dec. 21, 1999.

- [15] Xiaomin Kou; Corzine, K.A.; Familiant, Y.L.;, "Full binary combination schema for floating voltage source multilevel inverters," *IEEE Transactions on Power Electronics*, vol.17, no.6, pp. 891-897, Nov 2002.

- [16] Ounejjar, Y.; Al-Haddad, K.; Dessaint, L.A.; , "A Novel Six-Band Hysteresis Control for the Packed U Cells Seven-Level Converter: Experimental Validation," *IEEE Transactions on Industrial Electronics*, vol.59, no.10, pp.3808-3816, Oct.2012.

- [17] Silva, C.A.; Cordova, L.A.; Lezana, P.; Empringham, L.;, "Implementation and Control of a Hybrid Multilevel Converter With Floating DC Links for Current Waveform Improvement," *IEEE Transactions on Industrial Electronics*, vol.58, no.6, pp.2304-2312, June 2011.

- [18] Gupta, K.K.; Jain, S.; , "Topology for multilevel inverters to attain maximum number of levels from given DC sources," *IET Power Electronics*, vol.5, no.4, pp.435-446, April 2012.

- [19] Chung-Ming Young; Neng-Yi Chu; Liang-Rui Chen; Yu-Chih Hsiao; Chia-Zer Li, "A Single-Phase Multilevel Inverter With Battery Balancing," *IEEE Transactions on Industrial Electronics*, vol.60, no.5, pp.1972-1978, May 2013.

- [20] Rohner, S.; Bernet, S.; Hiller, M.; Sommer, R.;, "Modulation, Losses, and Semiconductor Requirements of Modular Multilevel Converters," *IEEE Transactions on Industrial Electronics*, vol.57, no.8, pp.2633-2642, Aug. 2010.

- [21] Mohan Ned, Undeland T.M. and Robbins W.P., "Power Electronics: Converters, Applications and Design." John Wiley and Sons, Second Edition, 2001.

- [22] Poh Chiang Loh; Holmes, D.G.; Lipo, T.A.; , "Implementation and control of distributed PWM cascaded multilevel inverters with minimal harmonic distortion and common-mode voltage," *IEEE Transactions* on *Power Electronics*, vol.20, no.1, pp. 90- 99, Jan. 2005.

- [23] Wenxi Yao; Haibing Hu; Zhengyu Lu; , "Comparisons of Space-Vector Modulation and Carrier-Based Modulation of Multilevel Inverter," *IEEE Transactions on Power Electronics*, vol.23, no.1, pp.45-51, Jan. 2008

- [24] Zhong Du; Tolbert, L.M.; Chiasson, J.N.;, "Active harmonic elimination for multilevel converters," *IEEE Transactions on Power Electronics*, vol.21, no.2, pp. 459- 469, March 2006.

- [25] Chiasson, J.N.; Tolbert, L.M.; McKenzie, K.J.; Zhong Du; , "Control of a multilevel converter using resultant theory," *IEEE Transactions* on Control Systems Technology, vol.11, no.3, pp. 345-354, May 2003.

- [26] K. K. Gupta and S. Jain, "Comprehensive review of a recently proposed multilevel inverter," in *IET Power Electronics*, vol. 7, no. 3, pp. 467-479, March 2014.

- [27] Angulo, M., Lezana, P., Kouro, S., Rodriguez, J., Wu, B.: 'Level-shifted PWM for cascaded multilevel inverters with even power distribution'. *IEEE Power Electronics Specialists Conf.*, 2007, pp. 2373–2378.

- [28] http://www.galco.com (Galco Industrial Electronics, Inc. 26010 Pinehurst Drive, Madison Heights, MI 48071).

- [29] Carnielutti, F.; Pinheiro, H.; Rech, C., "Generalized Carrier-Based Modulation Strategy for Cascaded Multilevel Converters Operating Under Fault Conditions," *IEEE Transactions on Industrial Electronics*, vol.59, no.2, pp.679-689, Feb. 2012.